「Meteor Lake」はCPUコアが3種類!? Intelが次世代CPUの詳細を発表(前編)

https://www.itmedia.co.jp/pcuser/articles/2309/20/news063.html

『2023年09月20日 00時35分 公開

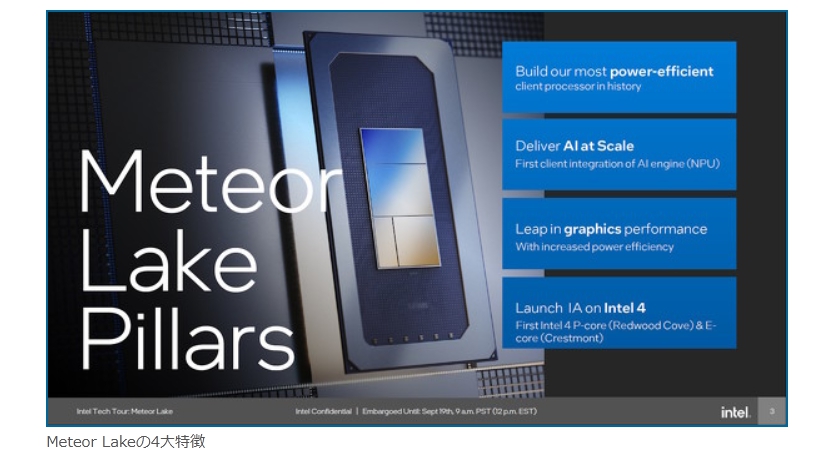

Intelは9月19日(米国太平洋夏時間)、12月14日(同)に正式発表される予定のモバイル向け次世代CPU「Core Ultraプロセッサ」(開発コード名:Meteor Lake)のアーキテクチャの詳細を発表した。

本CPUは、同社自身が「ここ40年間で最も大きなアーキテクチャシフトを行った」と公言している。それほどに“自信たっぷり”な製品のようだ。

その自身の裏付けは、民生向けCPUの製造技術における「初採用」の技術が数多く盛り込まれたことにある。筆者は発表に先駆けて技術説明会に参加したが、その内容は非常に興味深く、とても“濃い”ものだった。

そこで今回、前後編の2回に分けてMeteor Lakeの特徴を解説することにした。この記事(前編)では、読者の皆さんが一番関心を寄せているであろうMeteor Lakeにまつわる「製造技術」と「CPUコア」を中心に解説していきたい。

目次

Meteor Lakeを下支えする製造技術「Foveros」とは?

Meteor Lakeの「タイルアーキテクチャ」はどこがスゴい?

Compute Tile(CPUコア)は前2世代と大きく変わらず

SoC Tileにも「Eコア」 一体なぜ?

「3段変速」に挙動が変わったThread Director

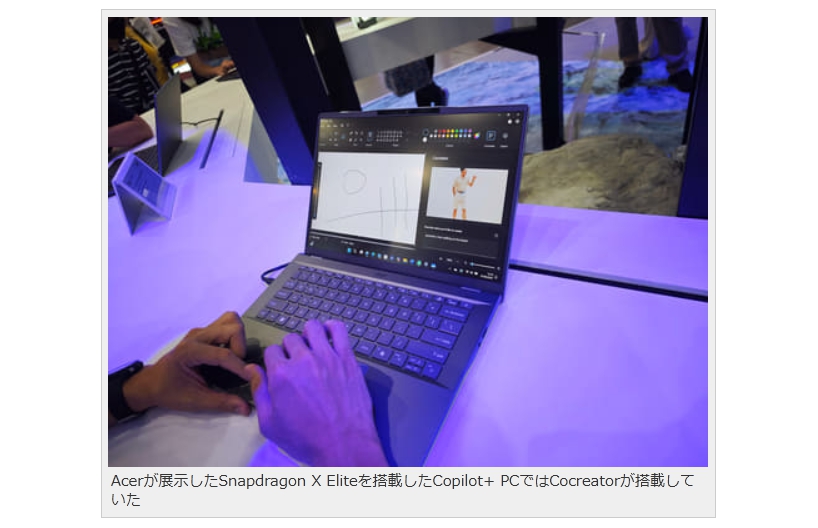

イメージ

Meteor Lakeのチップイメージ

5大特徴

Meteor Lakeの4大特徴

Meteor Lakeを下支えする製造技術「Foveros」とは?

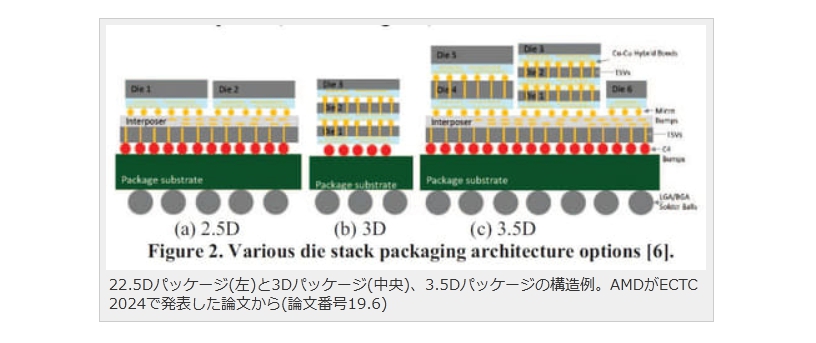

Meteor Lakeは、ユーザーの手元に届く製品となった際には「CPU」とか「プロセッサ」と呼ばれたりすることのなるだろうが、製品カテゴリーとしては、CPUを含む複数の機能を統合した「SoC(System on a Chip)」と呼ばれる半導体製品となる。

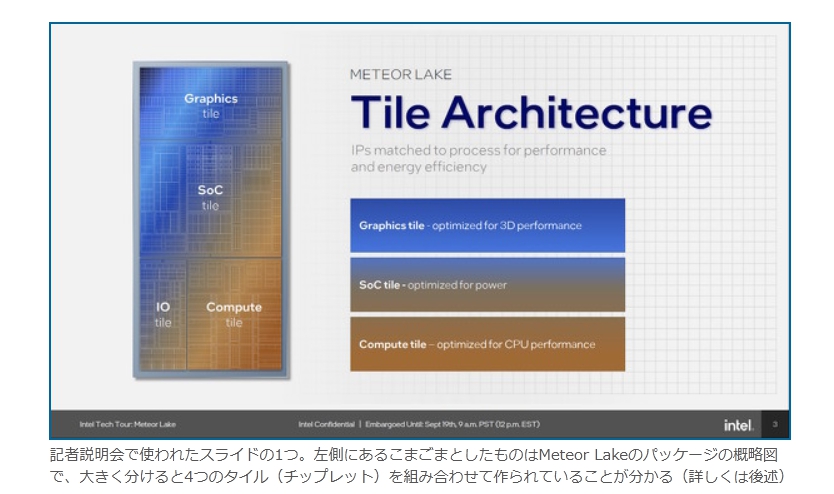

その最大の特徴は、IntelのSoCとしては初めて「タイルアーキテクチャ」を採用したことにある。タイルアーキテクチャとは、SoC(CPU)を単一のダイ(モノシリックダイ)として形成するのではなく、機能ごとに分かれた「機能ブロック」と呼ばれるダイを複数組み合わせて1つの「パッケージ」を作り、それを1つのSoCとして形成する手法だ。

機能ブロックは、小さなチップを意味する「チップレット」とも呼ばれる。そのこともあり、タイルアーキテクチャは一般的に「チップレット技術(アーキテクチャ)」と説明されることが多い。

チップレット

記者説明会で使われたスライドの1つ。左側にあるこまごまとしたものはMeteor Lakeのパッケージの概略図で、大きく分けると4つのタイル(チップレット)を組み合わせて作られていることが分かる(詳しくは後述)

チップレット技術によるCPU(SoC)の開発は、競合のAMDが「Zen 2アーキテクチャ」で既に実現している。Zen 2アーキテクチャといえば、2019年夏に登場したデスクトップ向けの「Ryzen 3000シリーズ」が初出なので、Intelはチップレット技術を「4年遅れ」で採用したともいえる。

しかし、Meteor Lakeにおけるタイルアーキテクチャを細かく見ていくと、IntelはAMDのチップレットよりも“先進度”の高いことに取り組んでいることが分かる。

説明中

Meteor Lakeのタイルアーキテクチャを下支えする「Foveros」という技術を解説するティム・ウィルソン氏(デザインエンジニアリンググループ バイスプレジデント兼SoCデザイン担当ゼネラルマネージャ)

少しややこしいのだが、Meteor Lakeにおけるタイルアーキテクチャは、「Foveros(フォベロス)」と呼ばれるダイ間積層配線技術によって実現している。

Foveros自体は全く新しい技術ではない。民生品向けとしては、2020年に登場したタブレットPC/2in PC向けCoreプロセッサ(開発コード名:Lakefield)で初採用されている。

しかし、このLakefieldは、レノボの初代「ThinkPad X1 Fold」など、幾つかのタブレットPCで採用はされたものの、採用事例は非常に少ない。そのせいか、量産開始から1年後の2021年には生産終了が告知されてしまった。Coreプロセッサファミリーの中でも、非常に短命な部類に入る製品だったともいえる。

Foverosの解説動画

ThinkPad X1 Fold

初代ThinkPad X1 Foldは、Lakefieldが採用された数少ない例

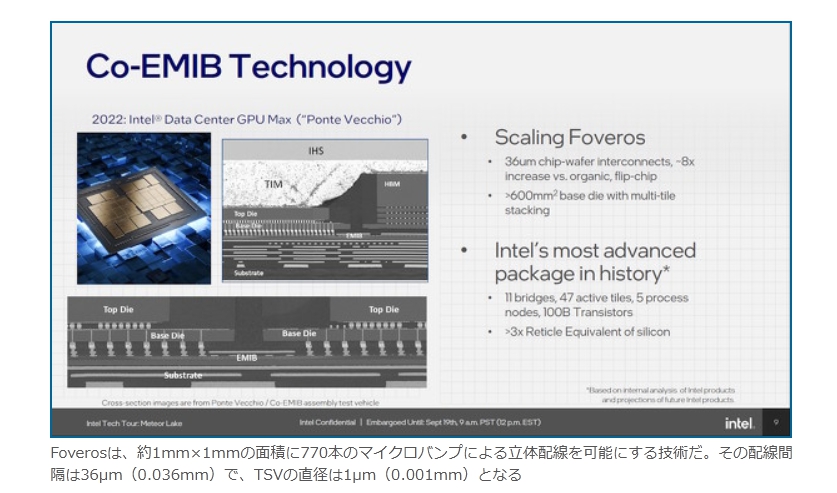

一度は消えたと思われたFoverosだが、Intelは「Intel Data Center GPU」(開発コード名:Ponte Vecchio)において再び採用し、量産実績を積み重ねてきた。

→ついに! ようやく? 「Intel Maxシリーズ」2023年1月から出荷 HBM付き「Xeon Max」と高密度実装GPU「Intel GPU Max」

Ponte Vecchioでの実績を通して、IntelはMeteor LakeでもFoverosを“使える”と判断したのだろう。

Foveros

Foverosは、約1mm×1mmの面積に770本のマイクロバンプによる立体配線を可能にする技術だ。その配線間隔は36μm(0.036mm)で、TSVの直径は1μm(0.001mm)となる

では、Meteor Lakeのタイルアーキテクチャは、従来のチップレット技術と何が違うのだろうか。』

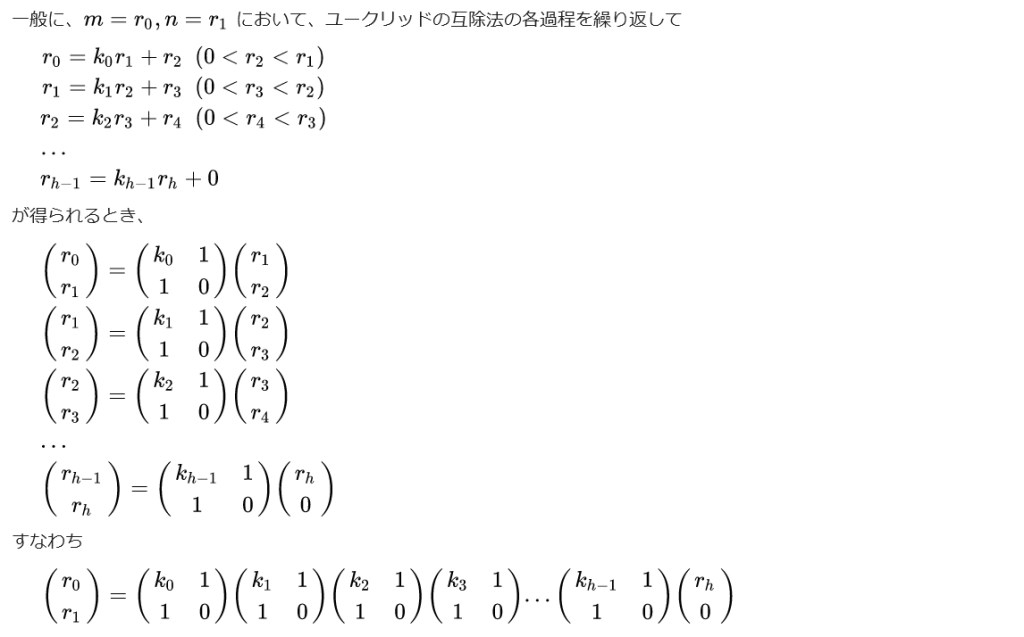

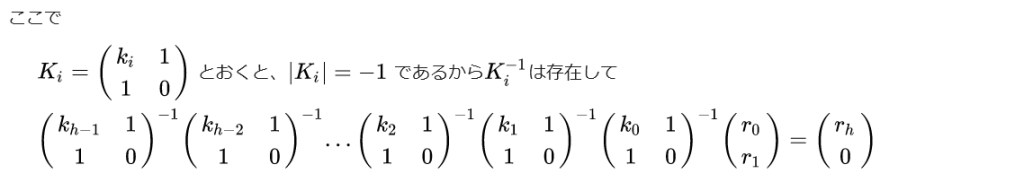

『Meteor Lakeの「タイルアーキテクチャ」はどこがスゴい?

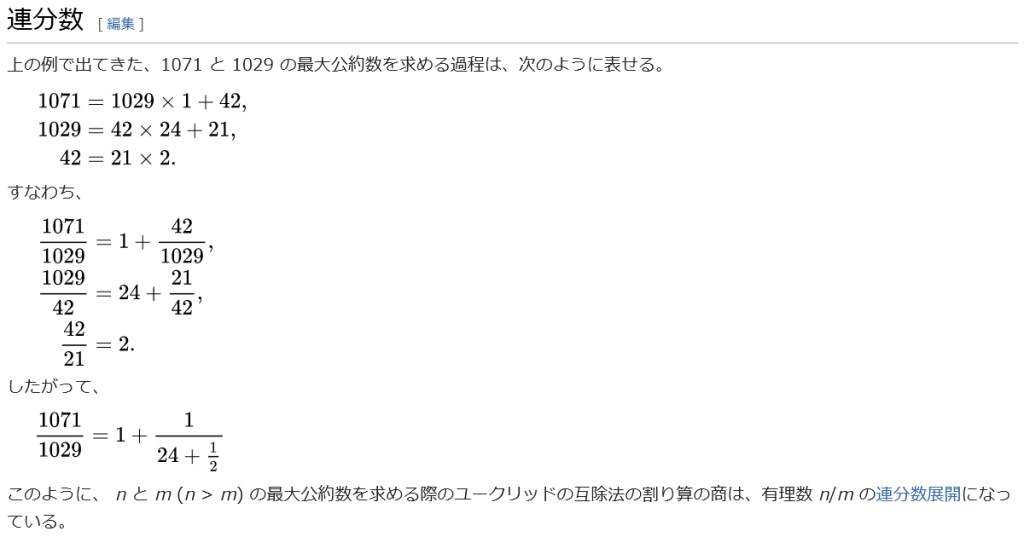

Meteor Lakeにおけるタイルアーキテクチャは、Foverosによって実現したもの。では、具体的に従来のチップレット技術と何が違うのだろうか。もう少し詳しく解説してみよう。

Meteor Lakeでは、主に微細な配線のみ施した「ベースダイ」の上に、機能別に形成されたタイル(チップレット)を載せている。このタイルたちは、ベースダイに対して「マイクロバンプ接合」を行ったり、要所要所ではベースダイを貫通する形で「TSV(Through-Silicon Via)配線」を行ったりしている。

従来のチップレット技術はパッケージ基板を介してチップレット同士を配線していたが、タイルアーキテクチャではベースダイを介してチップレットを接合させている。当然なのことながら構造は複雑となるが、見方を変えるとチップレットとの接合密度を高められる。ゆえに、ベースダイを介して接合されるチップレット間のデータ伝送速度(帯域)を格段に上げられるのだ。

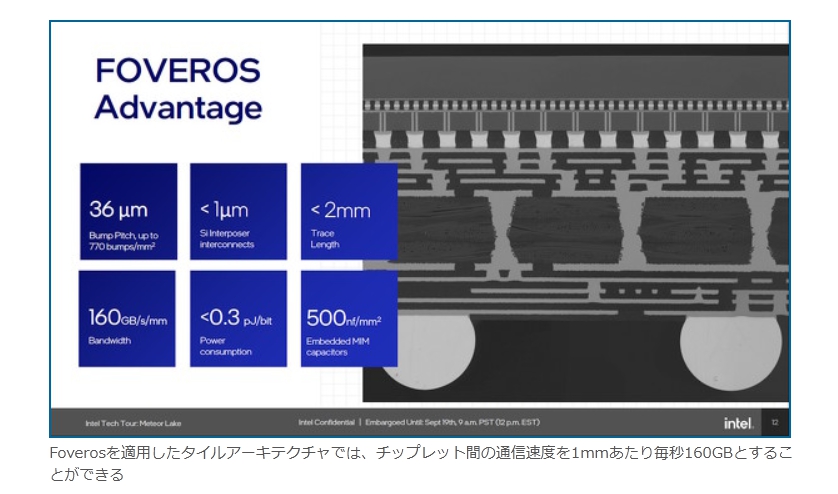

Foverosの優位性

Foverosを適用したタイルアーキテクチャでは、チップレット間の通信速度を1mmあたり毎秒160GBとすることができる

Intelでは各タイルを「機能名+Tile」のような名称で呼んでおり、Meteor Lakeでは以下のタイルをベースダイに集約することで1基のSoCを構成している。

Compute Tile(コンピュートタイル):CPUダイに相当

Graphics Tile(グラフィックスタイル):GPUダイに相当

I/O Tile(入出力タイル):各種入出力インタフェースを搭載

SoC Tile(SoCタイル):その他高機能部位を統合

タイルアーキテクチャで注目すべきなのは、各タイルのプロセスルール(微細度)は異なっても構わないという点だ。事実、Meteor Lakeの各タイルは、プロセスルールが以下の通り結構バラバラだったりする。

ベースダイ:22nmプロセス

Compute Tile:Intel 4(7nmプロセス)

Graphics Tile:TSMC N5(5nmプロセス)

I/O Tile:TSMC N6(6nmプロセス)

SoC Tile:同上

チップレット技術では先行しているAMDも、CPUダイとI/Oダイのプロセスルールは異なっていたので、このアプローチ自体は「できて当たり前」なのかもしれない。しかし複数のプロセスルールが混在しているタイルをベースダイに“直接”接合させる技術は間違いなく高度で、驚かされる。

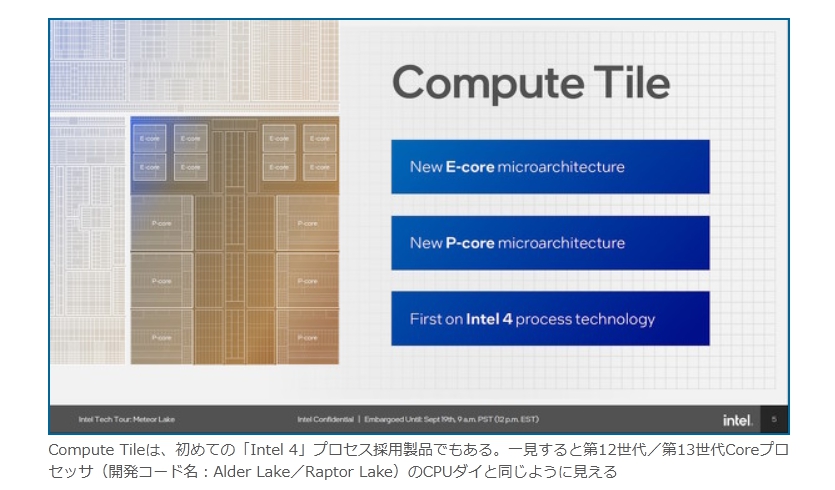

Compute Tile

Compute Tileは、初めての「Intel 4」プロセス採用製品でもある。一見すると第12世代/第13世代Coreプロセッサ(開発コード名:Alder Lake/Raptor Lake)のCPUダイと同じように見える

Meteor Lakeは4タイル構成だが、これらのタイルを別のものに入れ替えたり、あるいはベースタイルをより大規模なものに変更した上で、より多くのタイルを載っけたりすることで、CPUの「上位モデル」「下位モデル」の設計を比較的容易に行えることが、タイルアーキテクチャやFoverosの優位性――Intelはこう主張する。

拡張や縮小もおてのもの

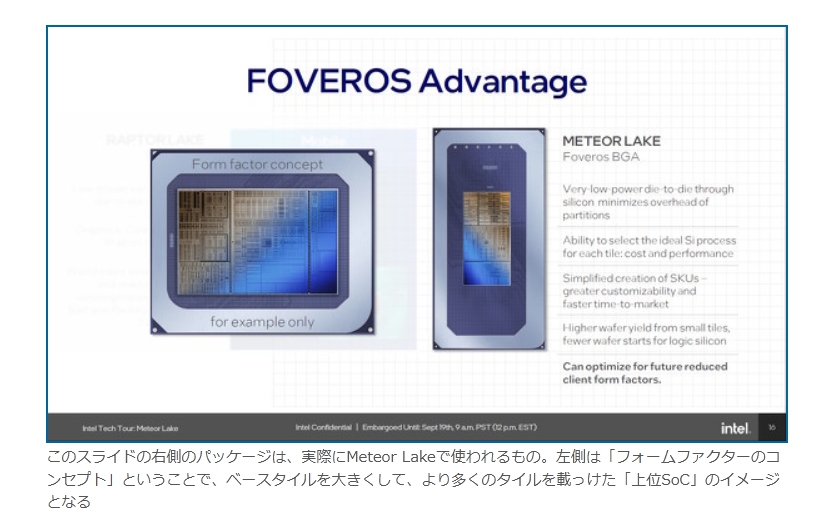

このスライドの右側のパッケージは、実際にMeteor Lakeで使われるもの。左側は「フォームファクターのコンセプト」ということで、ベースタイルを大きくして、より多くのタイルを載っけた「上位SoC」のイメージとなる

次は、Meteor Lakeの中でも特に注目したい部位「Compute Tile」と「SoC Tile」について詳しく紹介する。』

『Compute Tile(CPUコア)は前2世代と大きく変わらず

先述の通り、Compute TileはCPUダイに相当する。Meteor Lakeでは、処理性能重視の「高性能コア(Pコア、開発コード名:Redwood Cove)が最大6基、処理効率(省電力)重視の「高効率コア(Eコア、開発コード名:Crestmont)が最大8基実装される。

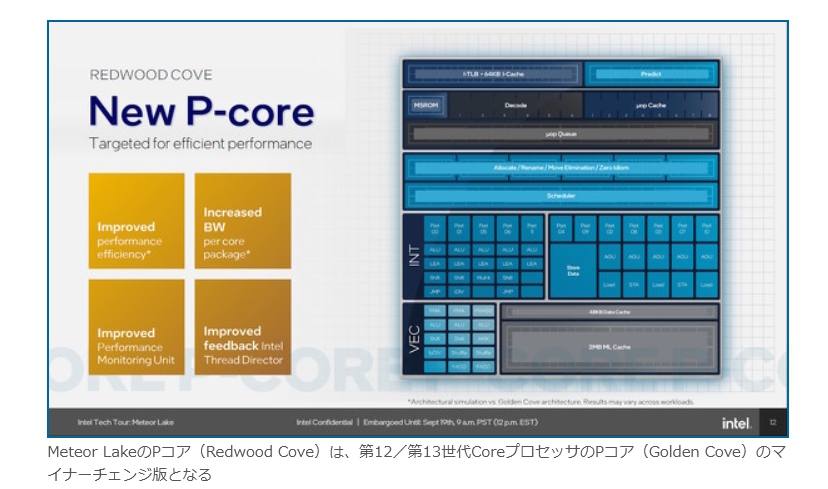

Redwood Coveは、第12/13世代CoreプロセッサにおけるPコア(開発コード名:Golden Cove)のマイナーチェンジ版だ。実効性能の改善は、L2キャッシュの増量による部分が大きい。Foverosによる高密度配線と、メモリ/キャッシュ帯域の拡大も性能アップに貢献しているそうだ。

なお、Redwood CoveはGolen Coveと同様にマルチスレッド(ハイパースレッディング)に対応している。OSからは1つの物理コアが2つの論理コアと見えるため、暇となっている実行ユニットを活用できれば1クロックで2倍の命令をこなせる。

Pコア

Meteor LakeのPコア(Redwood Cove)は、第12/第13世代CoreプロセッサのPコア(Golden Cove)のマイナーチェンジ版となる

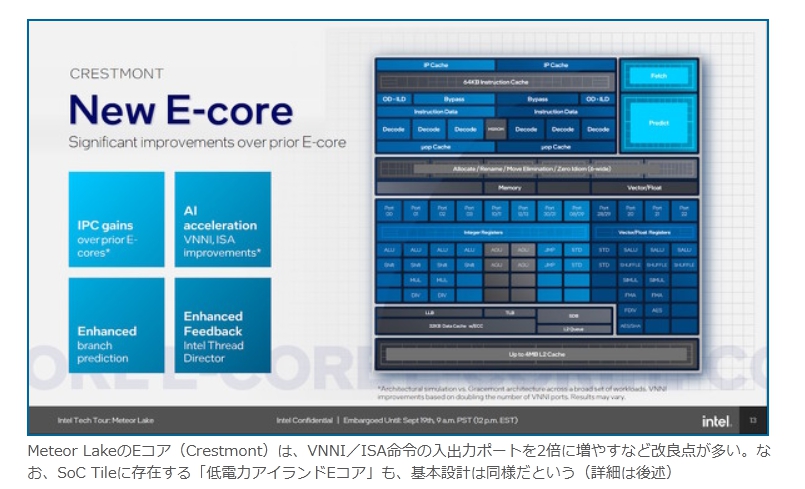

一方で、Crestmontは第12/第13世代CoreプロセッサのEコア(開発コード名:Gracemont)と比べると目立つ改良点が幾つかある。

まず、クロック当たりの命令実行効率は、先代比で4~6%も向上している。具体的な改善率の言及はなかったが、分岐予測のアルゴリズムを改善したことの効果だそうだ。また、ニューラルネットワークベースのAI(人工知能)プログラムでよく使われる「AVX-VNNI命令セット」の入出力ポートは2倍に増えている。恐らく、AI処理を多用するアプリが増えてきたことを踏まえた改良だと思われる。

なお、CrestmontはGracemontと同じく、マルチスレッドには非対応だ。

Eコア

Meteor LakeのEコア(Crestmont)は、VNNI/ISA命令の入出力ポートを2倍に増やすなど改良点が多い。なお、SoC Tileに存在する「低電力アイランドEコア」も、基本設計は同様だという(詳細は後述)

繰り返しとなるが、Meteor Lakeは最大で「Pコア6基12スレッド+Eコア8基8スレッド」という構成……なのだが、次に説明するSoCタイルにも別途Eコアが2基存在する。また、そのことに伴い、PコアとEコアに処理を割り振る「Intel Thread Director」の挙動に見直しが入っている。

SoC Tileにも「Eコア」 一体なぜ?

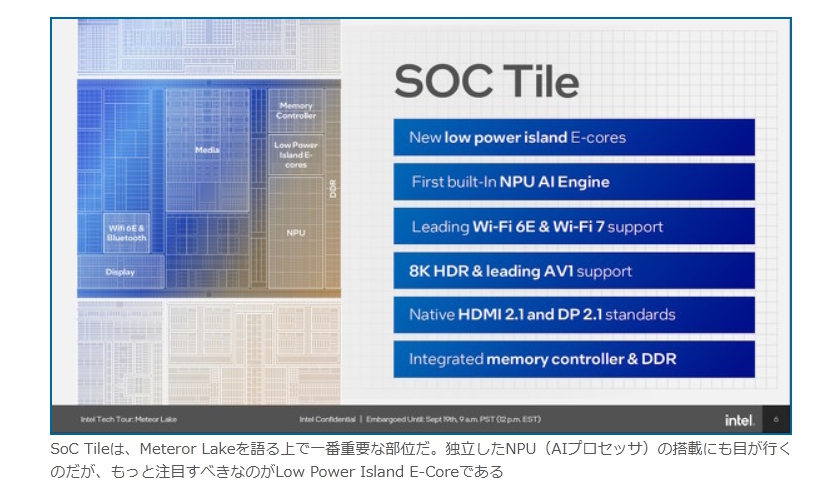

SoC Tileには注目点が多い。筆者としては、このSoC Tileが「Meteor Lakeらしさ」を一番形作っている部位だと思っている。

ブロック図を見るとあちこちに視線が行ってしまいがちなのだが、まず注目すべきはNPU(AIアクセラレーター)ではなく、「Low Power Island E-Cores」だ。

SoC Tile

SoC Tileは、Meteror Lakeを語る上で一番重要な部位だ。独立したNPU(AIプロセッサ)の搭載にも目が行くのだが、もっと注目すべきなのがLow Power Island E-Coreである

その名の通り、Low Power Island E-Cores(LP Eコア)はれっきとしたCPUコアだ。アーキテクチャ自体はCompute TileにあるEコアと同じで、Crestmontを採用している。

「なんでここにもEコアが?」というところだが、LP Eコアは最大2基2スレッド構成で、Compute TileのEコアよりも動作クロックがより低く抑えられている。「Low Power」の名の通り、クロックやコア数が少ない分、消費電力も少なくなっている。

Intelによると、PCの利用シーンでは普通のEコアですら性能が高すぎることも少なからずあるという。第12/第13世代Coreプロセッサは「Eコア→Pコア」の2段ギアだったのに対して、Meteor Lakeは「LP Eコア→Eコア→Pコア」の3段ギアとすることで、より効率的に稼働できるようにしたと考えれば分かりやすい。

Intelによると、LP Eコアだけが動員される場面は案外多いという。Compute Tileを休ませることで省電力性能を稼いでいるようだ。

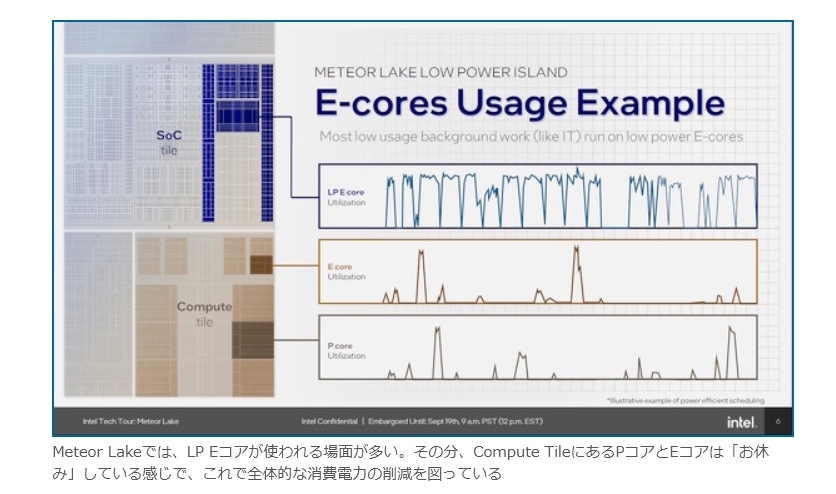

Eコアの使われ方

Meteor Lakeでは、LP Eコアが使われる場面が多い。その分、Compute TileにあるPコアとEコアは「お休み」している感じで、これで全体的な消費電力の削減を図っている

CPUコアはOSからはどう見える?

ということで、Meteor LakeのCPUコアは結局、最大で「Pコア6基12スレッド+Eコア8基8スレッド+LP Eコア2基2スレッド」となる。つまり最大16コア22スレッドのCPUなのだ。

ここでふと2つの疑問が浮かぶ。1つはこれらのCPUコアがOS(システム)からどう認識されるのか、もう1つはEコアとLP Eコアは同時稼働できるのかというものである。これら2点は、技術説明会でも質問が相次いだ。

Intelによると、16コア22スレッド構成のMeteor Lakeは、OSからも「16コア22スレッド」のCPUとして認識され、EコアとLP Eコアは同時稼働可能だという。特にLP Eコアは、SoC Tileにあるメディアエンジンとの相性が良いといい、「LP Eコアだけで動画再生をこなせる」と自信ありげに語っていた。LP Eコアも、そこそこの性能を備えていそうだ。

余裕

最大コア構成のMeteor Lakeを搭載したデモ機(MSI製)で動画を再生するデモンストレーション。タスクマネージャーのスレッド負荷率表示はほぼフラットだが、見事に動画を再生できていた。なお、最下段の右2つのグラフがLP Eコアが処理しているスレッドのものとなる

都合3種類のCPUコアを混載したこともあって、Meteor LakeではITDの挙動に変更が行われている。

「3段変速」に挙動が変わったThread Director

LP Eコアの解説を終えたので、ここからは後回しにしてきたIntel Thread Director(ITD)の挙動変更について説明しよう。

第12/第13世代Coreプロセッサでは、PコアとEコアに処理を割り振るための仕組みとしてITDが導入された。ITDはハードウェア(CPU)とソフトウェア(OS)の双方が協調して稼働することが特徴で、IntelはMicrosoftと協業し、Windows 11にITD対応のタスクスケジューラーを搭載している(※1)。

(※1)編集注:第12/第13世代Coreプロセッサでは、Googleとも協業して、ChromeOSにもITDを搭載している

レージャシューリー・チャブクスワー氏

新しいITDを解説するレージャシューリー・チャブクスワー氏(クライアントコンピューティング部門フェロー)

Meteor Lakeでは、新たにLP Eコアを含む3種類のCPUコアを搭載している。そのため、処理の割り振りを3種類のコアに行う必要が出てくる。そこで、今回もMicrosoftと協業し、Windows 11へとMeteor Lakeの「3段ギア」に対応するタスクスケジューラーを搭載する。

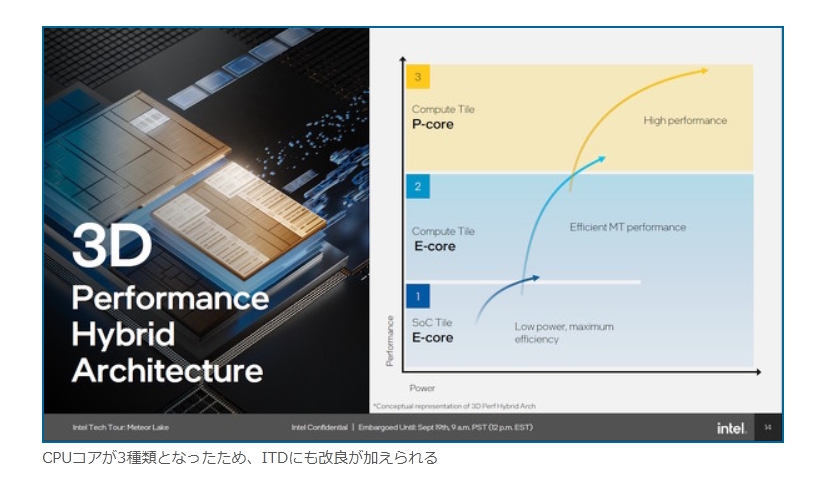

3段ジャンプ

CPUコアが3種類となったため、ITDにも改良が加えられる

CPUコア(スレッド)の割り当てアルゴリズムは、そのPCの使い方――例えば性能重視なのか、低消費電力重視なのか――で微妙に変わるそうだが、基本的には「高負荷ではないスレッドには、なるべくEコアやLP Eコアを割り当てる」という方針が適用されるという。

物理コアにしても論理コアにしても、スレッドの切り替え時には、大量のレジスタファイルの出し入れが行われる。ごくわずかではあるが、この工程は「処理の遅延」となる。それでも、スレッドの切り替えが頻繁(大量)に発生すれば、CPU全体で見た時のスレッドの実行効率は落ち混んでしまう。

もともと低負荷のスレッドであれば、Eコア側でまとめて実行させても、遅延の実害はないに等しい。ゆえに、新しいITDではこのような方針を取ることにしたそうだ。最初は極力LP Eコアにスレッドを振り、それでムリならCompute TileのEコアに移管し、それでもキツいならPコアにシフト……と、まさしく3段ギアによる「変速」を行っている。

この移管には、Windows 11のタスクスケジューラーから提供されるCPU負荷のリアルタイムレポートを参考にしているという。また、複数のPコアで負荷の低い処理をしている場合に、LP EコアまたはEコアがプロセスを“まとめて引き取る”制御も行うとのことだ。

これらの制御によって、Meteor Lakeは「最大性能」と「消費電力効率」を両立するのだ。

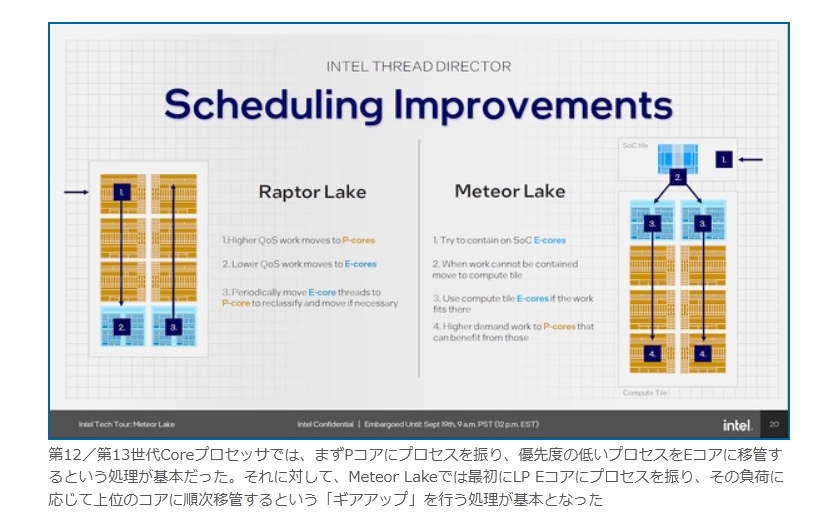

新旧Thread Directorの振る舞いの違い

第12/第13世代Coreプロセッサでは、まずPコアにプロセスを振り、優先度の低いプロセスをEコアに移管するという処理が基本だった。それに対して、Meteor Lakeでは最初にLP Eコアにプロセスを振り、その負荷に応じて上位のコアに順次移管するという「ギアアップ」を行う処理が基本となった

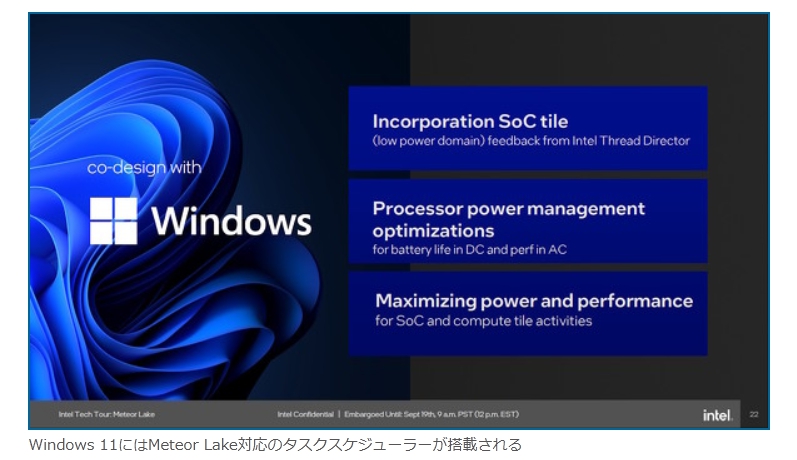

Windows

Windows 11にはMeteor Lake対応のタスクスケジューラーが搭載される

高効率の例

タスクスケジューリングの例

後編では、SoC Tileが備える他の機能と、Graphics Tile、I/O Tileの詳細を紹介する。

→後編の記事

(取材協力:インテル株式会社)

Copyright © ITmedia, Inc. All Rights Reserved.』