Intel、CPUやGPUを3次元積層する業界初の3Dパッケージング技術「Foveros」を発表、デモ

https://pc.watch.impress.co.jp/docs/news/1158136.html

『 笠原 一輝

2018年12月12日 23:00

米Intelは11日(現地時間)にIntelの共同創始者ロバート・ノイス氏のかつての私邸において記者会見を行ない、同社が開発している次世代CPUなどに採用される各種の技術を公開。Intelが開発してきた3Dダイスタッキング技術の「Foveros」を発表した。

従来の3Dダイスタッキングは、CPUやGPUなどのロジック回路とメモリなどを3次元に積層するものだったが、今回Intelが発表したFoverosは、メモリとロジックだけでなく、ロジックとロジックを3Dにスタッキングすることが可能になっている。Intelによればロジック同士による3Dダイスタッキングの技術は業界初で、2019年にはFoverosの技術を採用した最初のx86プロセッサをリリースする計画であることも同時に明らかにした。

業界初のロジックとロジックを3次元積層する3Dパッケージング技術「Foveros」

Intel上席副社長兼Intelアーキテクチャ/グラフィックスソリューション事業本部長兼エッジコンピューティングソリューション主任アーキテクトのラジャ・コドリ氏

Intel上席副社長兼Intelアーキテクチャ/グラフィックスソリューション事業本部長兼エッジコンピューティングソリューション主任アーキテクトのラジャ・コドリ氏は「現在はCPU、GPU、FPGA、アクセラレータなど複数のプロセッサがコンピューティング環境で利用されているヘテロジニアスな環境になっている。そうしたなか、パッケージングの技術の進化、とくに3次元積層技術が求められていた」と述べる。

Foveros

Foverosに使われている技術

そしてコドリ氏が公開したのが「Foveros」とIntelが開発コードネームで呼んでいる3Dパッケージング技術だ。3Dのダイスタッキングそのものは、これまでもGPUの上に、HBMメモリをスタッキングするなどのかたちで利用されてきた。一方、ロジックとロジックを積層する技術は業界初で、熱をどのように逃がすのかも含めて、さまざまな技術革新を盛り込んだ。

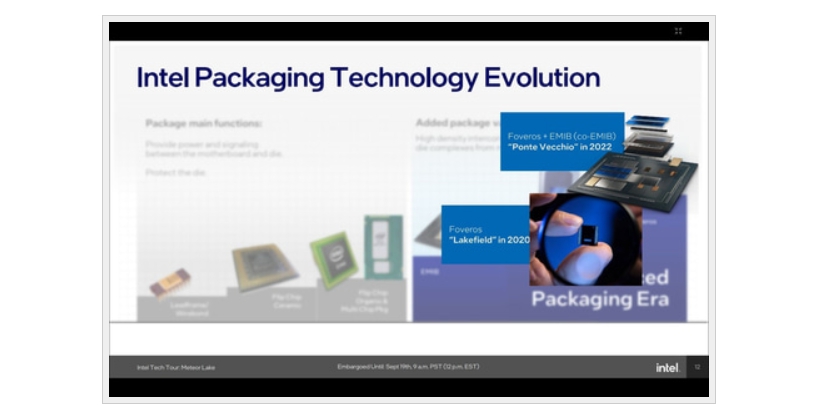

これまでのパッケージ技術の延長線上にFoverosがある

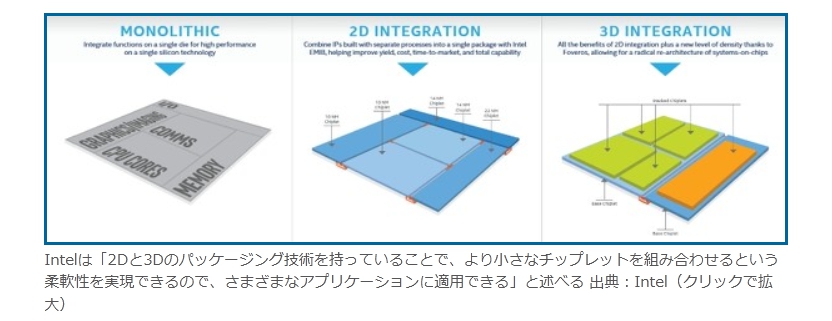

Foverosは、Intelがすでに投入しているEmbedded Multi-die Interconnect Bridge (EMIB)と呼ばれる2Dパッケージング技術の発展系になるものだ。Intelは開発コードネーム「KBL-G」など、複数のダイを1つのパッケージに統合する製品を近年推進しており、今回の3Dパッケージング技術はその延長線上にある。

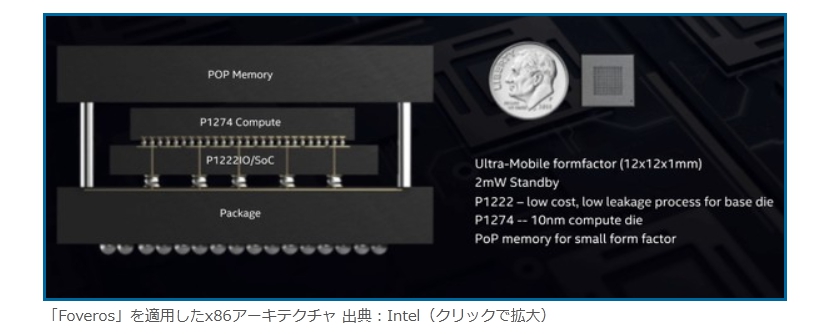

Intelが2019年に投入する予定のFoverosを利用した製品。下側に22nnmのSoC、その上に10nmのCPU+GPU、さらにその上にメモリがある構造、12x12x1mmという非常に小さなパッケージの中でロジックの3次元積層を実現している

Intelではこれを2019年の後半に実際の製品に投入する。最初のFoverosを活用した製品は、22nnmプロセスルールで製造されるSoC(x86プロセッサ+I/O)に、10nmプロセスルールで製造されるより強力な処理能力を持つx86プロセッサ+GPUと、その上にメモリを3段重ねにした製品で、アイドル時にはCPUが低消費電力で低リーケージで動作する22nnmプロセスルール側に切り替わり、低い電力で動作し、性能が必要な時には10nmプロセスルールの高性能なCPUに切り替わる仕組みになっている。

Foverosのデモ

下側のCPU4と表示されているのが10nm側のハイパフォーマンスプロセッサ、上側のCPU3は22nnmの高効率プロセッサ。負荷をかけたときだけCPU4が動くことがわかる

今回Intelはその最初の製品を実際に動かしてみせた。現在のエンジニアリングサンプルではファンが必要だが、実際の製品ではファンが必要ないぐらい低消費電力という。現時点ではこのFoverosに対応した製品がどのような市場に投入されるのかなどに関しては明らかにされていない。

Intelのホームページ

関連記事

Intel、高性能マルチダイチップ実現に向けた新パッケージ技術

2019年7月11日

後藤弘茂のWeekly海外ニュース

2020年代のIntel CPUのカギとなる新2.5D/3D積層技術