Arm、Cortex-X4やA720を発表。PC向けにX4×10+A720×4コア構成も可能

https://pc.watch.impress.co.jp/docs/news/event/1504067.html

『AIによる要約

英Armは、COMPUTEX TAIPEIの会場で、2023年向けPC・スマートフォン用SoCデザインIP群新製品TCS23を発表。CPUはCortex-X4、Cortex-A720、Cortex-A520に強化され、プライムコアCortex-X4は前世代比で15%性能向上、40%電力効率改善される。GPUは新しいアーキテクチャのImmortalis-G720が採用され、従来世代比でピーク性能と電力効率が15%向上、メモリ帯域の負荷が40%減少。さらに、クラスタコントローラDSU-120が提供され、14コア構成が可能に。CPUやGPUの性能向上が特徴のTCS23は、Armv9.2-Aに対応し、全体で64bitのみ対応する。今後の製品発表に期待が高まる。

この要約はChatGPTによって自動生成されたものであり、原文の完全性や正確性を保証するものではありません。この機能はベータ運用中です。

×』

『 笠原 一輝

2023年5月29日 09:30

Cortex-X4、Cortex-A720、Cortex-A520から構成されるTCS23のCPUクラスタ

英Armは、COMPUTEX TAIPEIが行なわれている台湾・台北市内の会場で記者会見を開催し、2023年のPCやスマートフォン向けSoCのデザインIP群新製品TCS23(Total Compute Solutions 23)を発表した。

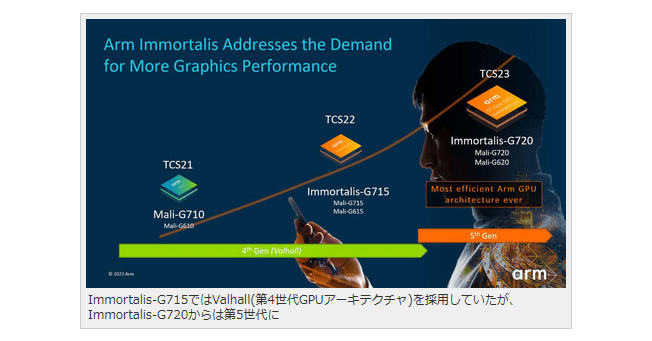

TCS23は、昨年(2022年)発表されたTCS22(CPUはCortex-X3、Cortex-A715、Cortex-A510、GPUはImmortalis-G715)から、CPUも、GPUも大幅に強化される。CPUはプライムコアがCortex-X4に、高性能コアがCortex-A720に、高効率コアがCortex-A520にそれぞれ強化される。プライムコアのCortex-X4は前世代に比較して15%性能が向上し、40%電力効率が改善される。

GPUのImmortalis-G720は同社が「第5世代」と呼んでいる新しいGPUアーキテクチャを採用しており、従来世代(Immortalis-G715)に比較してピーク時の性能と電力効率が15%、メモリ帯域への負荷が40%減少するとArmは説明している。

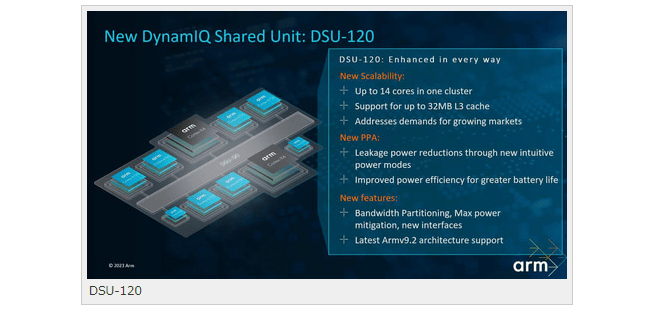

また、同社がDynamIQ Shared Uinit(DSU)と呼んでいるクラスタコントローラはDSU-120が新たに提供されることになり、Cortex-X4が10コア、Cortex-A720が4コアという14コア構成が可能になり、Arm版Windows(WoA)で高い処理能力を実現するPC用のSoCをデザインすることも可能になる。

Cortex-X4、Cortex-A720、Cortex-A520から構成されるTCS23のCPUクラスタ

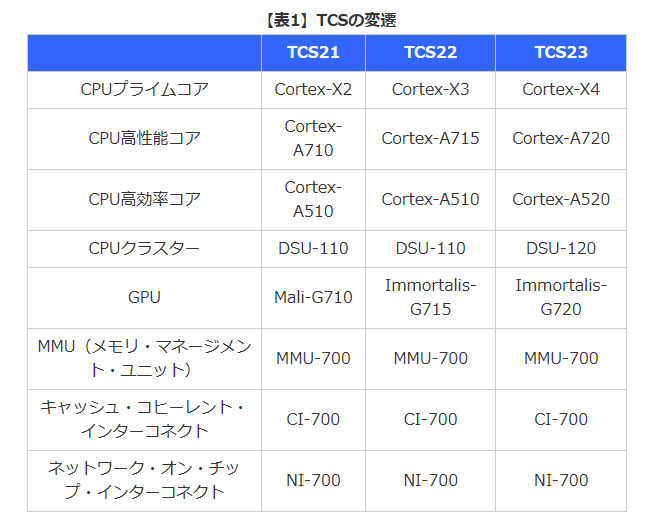

ここ数世代のCPUの進化

ここ数年、ArmはCPUやGPUのデザインIPを製品群として、1つのパッケージとして提供するようになっている(もちろん顧客となる半導体メーカーは単体のデザインだけを選択することも可能)。ArmではそうしたスイートをTCSと呼んでおり、毎年の新製品は西暦の下2桁の数字を冠して呼ばれる。2021年モデルであれば、TCS21、2022年モデルであればTCS22と呼んでいる。

【表1】TCSの変遷 TCS21 TCS22 TCS23

CPUプライムコア Cortex-X2 Cortex-X3 Cortex-X4

CPU高性能コア Cortex-A710 Cortex-A715 Cortex-A720

CPU高効率コア Cortex-A510 Cortex-A510 Cortex-A520

CPUクラスター DSU-110 DSU-110 DSU-120

GPU Mali-G710 Immortalis-G715 Immortalis-G720

MMU(メモリ・マネージメント・ユニット) MMU-700 MMU-700 MMU-700

キャッシュ・コヒーレント・インターコネクト CI-700 CI-700 CI-700

ネットワーク・オン・チップ・インターコネクト NI-700 NI-700 NI-700

そうして進化してきたArmのIP製品群最新版がTCS23となる。TCS23ではCPUも、GPUも、そしてCPUのクラスタを構成するコントローラとなるDynamIQ Shared Uinit(DSU)も更新されており、それによりSoC全体での性能が向上していることが大きな特徴となる。

Armのスマートフォン/PC向けCPU IPデザインは、プライムコア、高性能コア、高効率コアという3種類のCPUコアが用意されている。プライムコアのCPUコア数を増やせば性能を向上させることができるが消費電力は増え、逆に高効率コアを増やせば性能はそれなりだが、消費電力を減らすことが可能になる。

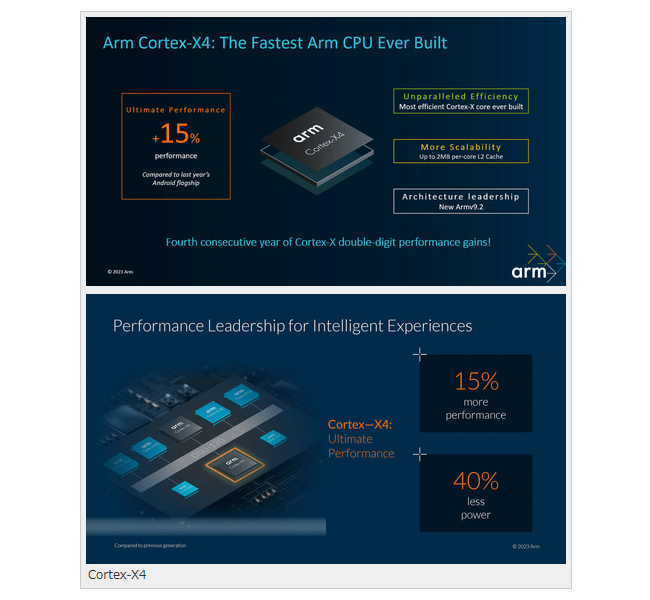

Cortex-X4

Armのプライムコアは、近年Cortex-Xのブランドで呼ばれており、2023年のモデルはCortex-X4になる。Cortex-X4の特徴はIPC(Instruction Per Clock-cycle)の向上にある。ArmはCortex-X4が前世代のCortex-X3と比較して、SPECRate2017_int_baseのピーク性能で15%向上しており、さらに電力効率では40%ほど改善していると説明している。

最近のArm CPU、特にAppleのMシリーズやAシリーズなどでは、シングルスレッドの性能が大きく引き上げられており、Cortex-X4でIPCが引き上げられたということは、シングルスレッドの性能もそれに合わせて引き上げられていることになる。なお、L2キャッシュに関しては1つのCPUコアあたり最大2MBの構成が可能になっている。

Cortex-A720

高性能コアはCortex-A720になる。以前の高性能コアはシングルスレッド時の性能を実現するCPUコアとして利用されていたが、現在はプライムコアがその役目を果たしているため、高性能コアは性能と消費電力のバランスをとりたいようなCPUコアとして選択されることになる。そのため、やみくもに性能を引き上げるという改良が加えられるのではなく、同じ消費電力で、より性能が向上する。そうした改良が加えられている。

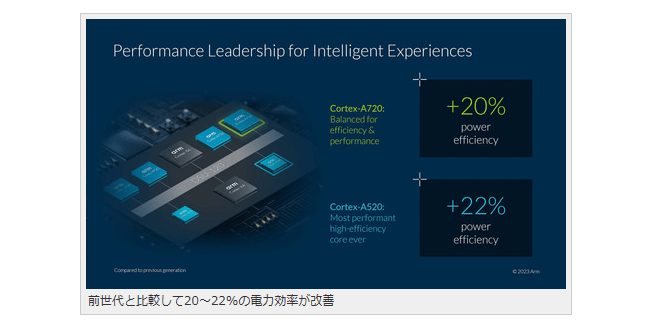

L1キャッシュは命令/データそれぞれが32KBないしは64KB、L2キャッシュは128KB、256KB、512KBから顧客が選択することが可能なことなどは従来世代と近似だ。ArmによればCortex-A715に比べて20%電力効率が改善している。

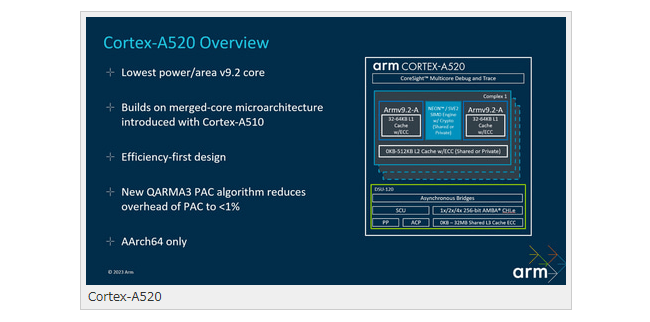

Cortex-A520

高効率コアのCortex-A520も同様で、前世代となるCortex-A510を元に、ダイに占める面積が22%削減されているのに、性能は8%向上している。1つのコンプレックスにつき2つのCPUコアがある構成になっており、コンプレックス単位でCPUコアを増やしていくことが可能になる。CPUコア1つあたりに32KBないしは64KBのL1データ/命令キャッシュ、コンプレックス1つあたりに0~512KBのL2キャッシュを実装することが可能になっていることなど基本的なアーキテクチャは従来製品と近似している。ArmによればCortex-A510に比べて22%電力効率が改善している。

前世代と比較して20~22%の電力効率が改善

高効率コアも64bitのみになり、32bit互換性はなくなり、性能や電力効率が向上

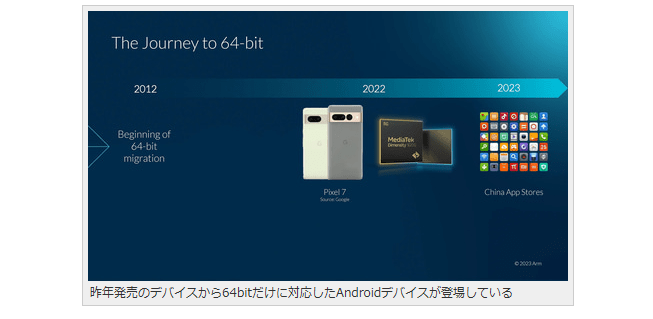

昨年発売のデバイスから64bitだけに対応したAndroidデバイスが登場している

こうしたTCS23の大きな特徴は、3種類すべてのCPUが命令セットアーキテクチャはArmv9.2-Aに対応し、64bit(AArch64)のみに対応していることだ。というのも、TCS22では高効率コアのCortex-A510が32bit(AArch32)にオプション(つまり半導体メーカーが32bit実装することが可能だった)で対応していたが、Cortex-A520では64bitのみに変更されているからだ。

プライムコアと高性能コアに関してはCortex-X3およびCortex-A715で既に64bitのみになっており、今回Cortex-A520が64bitのみとなったことで、TCS23全体で64bitのみに対応することになる。

このことはAndroidプラットフォームが、32bitを廃止して64bitへ移行しようとしている流れと連動している。Googleが昨年発表したPixel 7シリーズは64bitのみに対応しているほか(ただしCPUのアーキテクチャとしては32bitにも対応している)、同じく昨年MediaTekが発表したDimensity 9200に関しては、Cortex-X3+Cortex-A715+Cortex-A510になっており、ハードウェアとしては64bitのみに対応するようになっている。

ArmV9.2では複数の命令が追加されている

実際、Googleは開発者に対して64bitアプリへの移行を促しており、現時点では主要なアプリケーションに関しては64bitへの移行が済んでおり、フリーソフトなどで更新がとまっているようなものだけが32bitのままという現状になっている。このため、既にAndroid OSのデバイスとしては64bitのみで問題ないというのがArmの基本的な考え方になる。

Armが64bitへの移行を進める背景には、32bitの互換性を残しておくことが、性能競争の観点から不利になる可能性があるからと考えていると推察できる。32bit命令に対応するためには、ダイにそのためのエリアを残さないといけず、ダイサイズの肥大化を招くことになるし、その結果として消費電力も増えることになる。

実際、Appleは、Aシリーズの64bit化を、Androidよりも早く実現しており、それがAシリーズの高性能につながっていることを指摘する関係者は少なくない。その意味でも、Android陣営も早期に64bit化を実現することが求められていたのだ。

ただし、その結果として32bitとの互換性はなくなるので、64bit版がないアプリケーションやOSは動作できなくなる。Android OSとGoogle Playストアで配布されるアプリに関しては既に64bit化が済んでいるのでほぼ問題ないと言えるが、組込系のOSやアプリケーションなどではまだまだ32bitの互換性を必要とする場合があると考えられる。実際、Qualcommは、現行製品のSnapdragon 8 Gen 2の高性能コアをCortex-A715とCortex-A710を2コアずつ搭載している4コア構成にしている。

関連記事

【笠原一輝のユビキタス情報局】TSMCの4nmで製造され、ユニークな構成のCPUを内蔵するSnapdragon 8 Gen 2、GPUの大きな性能向上を確認

Snapdragon 8 Gen 2に関してはコンシューマ向けなので、高性能コアがすべて64bitでも特に不都合はないと考えられるが、Qualcommはそうしたコンシューマ向けのSoCを将来的に組込向け(たとえば自動車やIoTなど)に横展開するのが通例であるため、こうした構成になっていると考えられる。

その意味で、そうした戦略をとっているQualcommなどにとっては、2023年の末に発表されると予想される来年向けの「Snapdragon Gen 3」(?)でどのようなデザイン構成を取るのかは注目したいところだ。

レンダリング時の手法を見直してメモリ帯域への圧迫を改善するDVSなど第5世代GPUアーキテクチャを採用

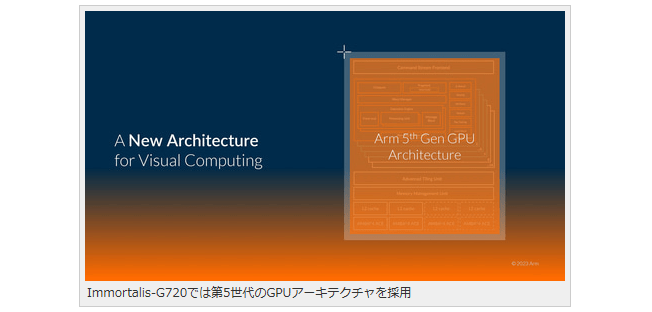

Immortalis-G720では第5世代のGPUアーキテクチャを採用

TCS23のもう1つの大きな目玉は新しいアーキテクチャを採用したGPUとなるImmortalis-G720だ。昨年Armが発表したImmortalis-G715、一昨年(2021年)のMali-G710は、Armが「Valhall」(バルホール)という開発コードネームで呼ばれていた同社の第4世代GPUアーキテクチャがベースになっていた。

Valhallアーキテクチャは、2019年に発表されたMali-G77で導入されたタイルベースのGPUアーキテクチャで、画面のピクセルを一定規模のタイルに分割してそれぞれのタイルをレンダリングしていくタイプのGPUになる。こうしたタイルベースのレンダリングは、モバイルGPUでは一般的に利用されている手法で、以前はやはりモバイル向けGPUでは主流だったPowerVRのGPU(AppleのAシリーズでかつて採用されていた、現在はApple自社製GPUに切り替えられている)などでも採用されていたものだ。

Immortalis-G715ではValhall(第4世代GPUアーキテクチャ)を採用していたが、Immortalis-G720からは第5世代に

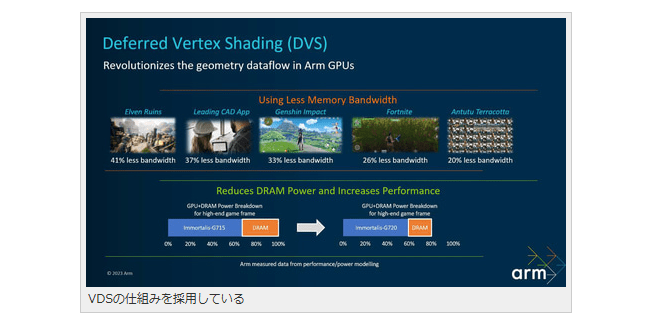

今回Armが発表したImmortalis-G720は、そのValhallの後継となる第5世代GPUアーキテクチャを採用している(なお、Armによればこの世代ではなぜかアーキテクチャの開発コードネームは公開しないことにとのことだ、このため以下第5世代GPUアーキテクチャとだけ呼ぶことにする)。第5世代GPUアーキテクチャの最大の特徴はDVS(Deferred Vertex Shading)と呼ばれる、メモリ帯域への負荷を減らす手法が採用されていることにある。

タイルベースアーキテクチャのGPUでは、一般的にバーテックスシェーディングと呼ばれるレンダリングする前に各頂点の頂点座標を演算し、その後で色を塗りつぶしていくフラグメンテーションという2段階で処理が行なわれる。

このため、バーテックスシェーディングの段階でメモリからデータを出し入れし、フラグメンテーションでもメモリの出し入れが発生する。つまり、2度メモリへアクセスが行なわれるため、それがメモリ帯域を圧迫することになり、性能低下の発生、そしてメモリへのアクセスが頻繁に発生することで消費電力も増えることになる。

VDSの仕組みを採用している

そこで、VDSではDeferred(遅延)という言葉に象徴されるように、バーテックスシェーディングの処理をフラグメンテーションが行なわれる段階まで遅らせる。それにより、メモリへのアクセスは1回になり、メモリアクセスの効率が改善する。VDSによりメモリ帯域への圧迫は減少し、GPUの性能も、そして消費電力も減らせる。

Armによれば、このVDSにより「Elven Ruins」で41%、「Genshin Impact」で33%、Fortniteで26%のメモリ帯域削減効果があるという。また、CADのようなアプリケーションでも有効で37%の削減効果があるとArmは説明している。

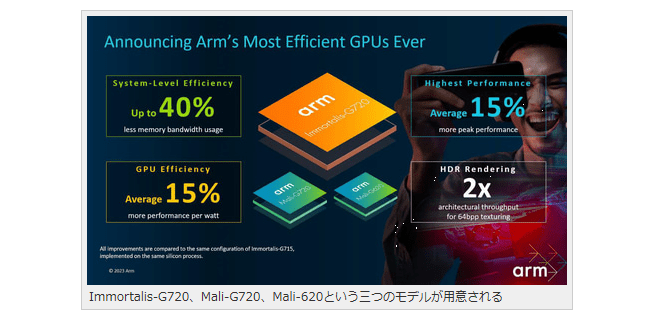

Immortalis-G720はGPUの演算器は10コアないしはそれ以上の構成が可能になっており、顧客の性能ニーズに合わせた実装が可能になる。同時に発表されたMali-G720は6~9コア、Mali-G620は5コアないしはそれ以下の構成が可能で、GPUの性能がImmortalis-G720ほどは必要ではない場合にはそちらを選択することが可能だ。

Immortalis-G720、Mali-G720、Mali-620という三つのモデルが用意される

ArmはImmortalis-G720、Mali-G720/620はいずれも従来世代と比較して電力効率が15%以上改善されており、かつメモリ帯域への負荷が40%削減され、ピーク性能では15%向上していると説明している。

最大14コア/32MB L3キャッシュという構成も可能になり、デスクトップPC向けCPU並の構成を実現

DSU-120

ArmアーキテクチャのCPUは「クラスタ」という考え方により構成されるのが一般的で、かつてはbig.LITTLE、現在はDynamIQと呼ばれる複数の種類のCPUにより1つのクラスタが構成されるようになっている。TCS23で言えば、シングルスレッドの性能を重視したプライムコアがCortex-X4、性能と電力のバランスをとった高性能コアがCortex-A720、電力効率重視の高効率コアがCortex-A520という3種類のCPUコアが用意されているのは説明した通りだ。

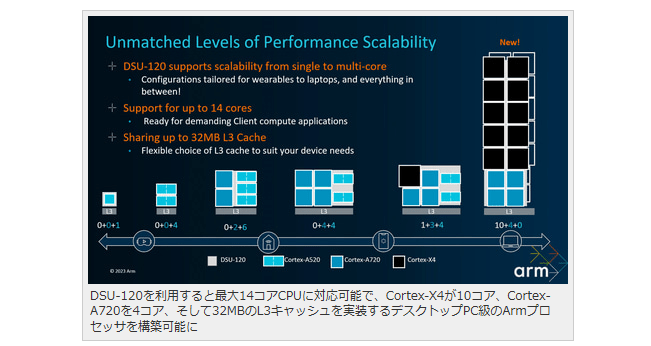

DSU-120を利用すると最大14コアCPUに対応可能で、Cortex-X4が10コア、Cortex-A720を4コア、そして32MBのL3キャッシュを実装するデスクトップPC級のArmプロセッサを構築可能に

そうしたクラスタを構成するためのコントローラをArmはDSU(DynamIQ Shared Uinit)と呼んでおり、TCS22まではDSU-110が提供されており、最大で10コア構成までが可能になっていた。

しかし、今回のTCS23ではその改良版となるDSU-120が導入される。このDSU-120では最大で14コアまでの構成が可能になっており、Cortex-X4を10コア、Cortex-A720を4コアで、合計14コアでL3キャッシュが32MBになるArm版Windows(WoA:Windows on Arm)向けの実装などが可能になるという(もちろん消費電力を無視すれば、それをスマートフォン用として投入することも不可能ではない)。それだけのスペックであれば、IntelやAMDのデスクトップPC向けのCPUに匹敵するような性能を実現する可能性が出てくると言える。

ただし、Arm版Windows向けにSoCを投入している唯一のベンダーであるQualcomm(MicrosoftブランドのSQ3も同社の設計・製造)は次世代のPC向けSoCに「Oryon」(オライオン)の開発コードネームで知られる自社設計のArm CPUを搭載する計画を明らかにしている。

関連記事

新CPU「Oryon」で、Snapdragon搭載Windowsデバイスの普及に向けて2024年は転換点に

このため、そうしたCortex-X4 10コア+Cortex-A720 4コアというArm版Windows向けSoCを設計するベンダーは今のところないのが現状で、MicrosoftがMediaTekなどほかのArm SoCベンダーとの協業を明らかにするか、あるいは自社設計のSQシリーズをQualcommベースからArm IPベースにでも変更しない限りは市場に登場するのは難しいと考えられる。そのため、そうしたハイエンド向け製品は、MediaTekが大きな市場シェアを持つChromebook向けとして採用される可能性が高いのではないだろうか。

来年のプライムコアはBlackhawkに、TCS23を搭載したスマートフォン用SoCは今年末に登場か?

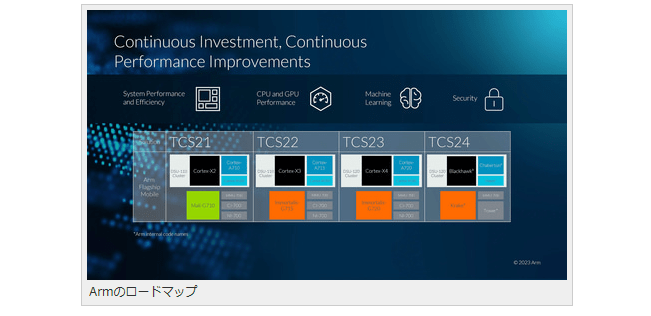

Armのロードマップ

Armは来年のTCS24の計画に関しても説明している。CPUに関してはプライムコアがBlackhawk(ブラックホーク)、高性能コアがChaberton(シャバートン)、高効率コアがHayes(ヘイズ)に、GPUはKrake(クラック)と開発コードネームで呼ばれる製品に進化する計画だ。

TSMCのN3E(3nmプロセスノード)に最適化済み、テストチップも既にテスト生産済み

Armによれば、既にこうしたTCS23は同社の顧客である半導体ベンダーに対して情報を公開済みで、TCS23の設計データを利用した製品を設計することが可能になっているという。また、Cortex-X4のテストチップは、TSMCのN3E(3nmプロセスノード)でテスト製造が行なわれており、TSMCの3nmノードへの最適化なども既に済んでいるとArmでは説明している。

昨年のTCS22が、いずれも11月に発表されたQualcommのSnapdragon 8 Gen 2、MediaTekのDimensity 9200に採用したことを考えれば、本年のTCS23を採用した製品もそうした年末のタイミングに発表される可能性が高いと言える。 』